電子ペーパー実験セットで使っている、E-INK製のED050SC3やED060SC4の電子ペーパーは、データバスと制御信号含めて15本の信号線が必要です。また、電源の制御も含めてあと数本の信号線が必要です。このため、マイコンで電子ペーパーを制御するためには20本くらいのGPIOピンが必要となります。

インターネットに接続できる便利なマイコンESP-WROOM-02を使おうとすると、IOピンが少なく制御することができません。このため、電子ペーパー実験セットでは、シフトレジスターを使ってSPI信号から16bitのパラレル信号に変換して、制御しています。

少ないIOしかないマイコンで、今まで以上にスイッチを追加したり、電源制御を詳細に行うなどの機能拡張を行う場合、74HC595などの汎用のロジックICや、PCF8575などのIOエキスパンダICを多用することが考えられますが、回路の規模が大きくなってしまいます。

また、ESP-WROOM-02のSPIは40MHzで動作しますが、GPIOは数MHzしか出ません。電子ペーパーの解像度は800x600ドットとデータが膨大なため、GPIOを利用した制御では描画速度に限界があり、もう少し改善したいところです。

小規模CPLD 5M160Z

これらを解消できるかもしれないのがCPLDです。CPLDは自由に設計できるロジックICのようなもので、例えば20bitのシフトレジスターを作ったり、8クロックごとにパルスを出す回路を作ったりと、オリジナルのデジタルICを作れます。しかも、マイコンにプログラムをするような手軽さです。

CPLDとほぼ同じICにFPGAがありますが、こちらは大規模な回路を作ったり、大量のIOを使ったり、超高速で動作したり、部品が高かったりと、高性能すぎて今回の規模ではオーバースペックです。ちょこっとだけ、独自のロジック回路が欲しい、そんな時にCPLDです。

Intel MAX Vシリーズ

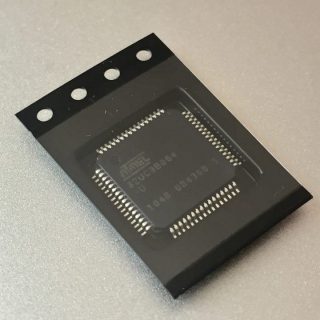

44ピンから64ピン程度のQFPパッケージで、数100円で購入できるお手頃なCPLDを探したところ、IntelのMAX Vシリーズを発見しました。

パッケージは64ピンの0.4mmピッチのEQFPです。このパッケージで一番たくさん回路が入るデバイスは5M160Zというものになります。

128個のマクロセルが入っているので、最大128ビットのカウンタくらいが作れる規模ということですかね。

IOピンは54本

64ピンパッケージの場合、IOは最大で54本です。今回の用途では30本くらいあればいいので、十分です。

電源は1.8V

今のデバイスは省電力化していて、このデバイスはコア電圧1.8Vで動作します。AVR32のボードを作った時もコア電圧は1.8Vでした。

AVR32は1.8Vのレギュレータがマイコンに内蔵されていましたが、MAX Vは内蔵されていません。自分で用意する必要があります。

IOはレベルシフタ内蔵で自由に設定可能

コアは1.8Vでいいですが、IOは3.3Vで動作させたいです。MAX Vはレベルシフタが入っていて、IO用の電源を用意することで、その電源電圧のIOとして動作します。3.3 V、2.5 V、1.8 V、1.5 V、1.2 Vの電圧に対応しているので、コアは1.8VだけどIOは3.3Vといった動作が可能です。

評価ボードの設計

5M160の評価ボードが市販されていないか探したのですが、ありませんでした。ないのであれば作ってしまいましょう。

ピンの種類

MAX® V Device Family Pin Connection Guidelinesの資料によると、以下のように分類されます。

- コア電源ピン(VCCINT)

2ピンあり1.8Vを供給します - IO電源ピン(VCCIO[1:2])

IOピンはバンクという大きく2つに分かれていて、バンクごとにIO電圧を個別に設定できます。例えばバンク1のIOは3.3V、バンク2のIOは2.5Vといった使い方ができます。今回はどちらも3.3Vで設計します。 - GND

GNDピンはなくIC背面のパッドがGNDになっています。手半田では実装が難しいですね。 - クロック(CLK[0:3])

CPLD内部でクロックを使いたい時に外部クロックをつなぐピンです。汎用IOとしても利用可能。MAX Vは内蔵クロックがあるので、正確なクロックが必要な場合に利用する感じかな。 - JTAGピン

TCK 1kΩでプルダウンする

TMS 10kΩでプルアップする

TDO 10kΩでプルアップする

TDO 特に指示なし(色々な回路を見るとプルアップされていることが多い) - リセットピン(DEV_CLRn)

あらかじめ設定することで、Lowでデバイスをリセットするピンになる。汎用IOとしても利用可能。資料ではどちらの機能としても利用しない場合にはプルダウンすることを勧めている。 - イネーブルピン(DEV_OE)

あらかじめ設定することで、Lowで全ての出力ピンをハイインピーダンスすることがてきるピンになる。汎用IOとしても利用可能。資料ではどちらの機能としても利用しない場合にはプルダウンすることを勧めている。 - IOピン

差動動作ができるピンもある。(今回はそこまで求めない)

ブロック図

USBを電源として、3.3V、1.8Vのレギュレータで電源を生成します。あとは、JTAGと各バンクごとのIOをコネクタに出します。とてもシンプルですね。

回路図

KiCadで回路図を描きます。3.3VのレギュレータはAVR32のボードを作った時にも使った超ロードロップのADP3338を使いました。1.8VはXC6206の1.8Vレギュレータを使いました。このレギュレータは100mA出力時に250mVのドロップですみます。3.3Vから1.8Vを生成しても安定して使えます。

あとは、動作確認用に4つLEDをつけました。

アートワーク

電源を手動で配線して、あとはオートルーターにお任せ。それほど難しくなかったのか数10分で終了。オートルータの配線結果を手動で整形します。この整形には時間がかかります。

面つけ

今回もSeeedStudioのFusionPCBに注文します。10cmx10cmのサイズに今回の評価基板が2枚取れるので、pcbnewで面つけします。

発注

SeeebStudioに基板とステンシルを発注します。3月いっぱいは割引きクーポンを使うと20%割引きになるので、少し安く発注できました。

注文時に「Fusion20」と入力すると、割引きされます。送料は安くならなかったです。

部品も発注したので、それぞれ届いたら製作したいと思います。届くのは3週間くらい先かな。

2019.4.16届きました。続きはこちら

ここで作ったCPLD実験セットがこちらより↓↓購入できます。

コメント