以前MAX V CPLDボードを作りました。

このCPLDで音源ICを作ろうとしたところ、和音を出すには容量が小さくてプログラムできませんでした。そこで、MAX 10 FPGAを使って音源を作っています。

「FPGA電子工作スーパーキット」という書籍に付いてくるMAX10 FPGAが載ったFPGAボードを使っています。

これはこれでいいのですが、LE数が8000もあるので、音源ICにはかなり余裕すぎる容量です。また、色々なICをつなぎたいので、たくさんIOピンがあるといいのですが、「FPGA電子工作スーパーキット」のボードは一部のIOピンしか端子に出ていません。

FPGA、電源、ほとんどのIOがピンに引き出されている、だけのシンプルな構成のFPGAボードが欲しくなりました。案外こういったシンプルだけど、ピンがいっぱい引き出されてる評価ボードってないんですよね。

MAX 10 10M02 FPGA

程よい容量のFPGAを探す

以前作ったCPLD(LE数160)よりも多くて、MAX10のLE数8000よりも少ない、FPGAに、MAX10シリーズの 10M02 というLE数2000のFPGAがあります。「FPGA電子工作スーパーキット」に付いてくるFPGAと同じMAX 10 シリーズの中の、最小容量のモデルになります。

MAX V CPLDシリーズの大容量版も検討したのですが、MAX 10 FPGAシリーズの低容量版よりも、MAX V CPLDシリーズの大容量版の方が高かったので、安価なMAX 10シリーズにしました。

10M02というモデルの中には、BGAパッケージや、QFPパッケージなどパッケージの違いや、必要な電源の数の違いなど、数種類のモデルがあります。

今回は、「FPGA電子工作スーパーキット」に付いてきたFPGAと同じ、QFPパッケージの「10M02SCE144C8G 」にします。単電源で動作し、QFPパッケージは半田付けしやすいですからね。

KiCadのライブラリを作る

10M08のライブラリはネットにあったのですが、10M02は無かったので自作します。まずは、ピンアサインを知りたいのですが、データシートには書いてありません。どうやらピンアウトというのが、ピンアサインであることがわかりました。

このページのMAX 10のところを開いて、10M02SCの中のPDF、テキスト、エクセルの各ファイルをクリックすると、ピンアサインのファイルがダウンロードできます。

10M02SCのE144というのが目的のパッケージのピンアウトです。

この情報をもとに、シンボルエディタでバンクごとにシンボルを作りました。

フットプリントは、SnapEDAというところから10M08SAE144C8Gのフットプリントがあったので、ダウンロードしてこれを使ってみようと思います。

KiCad用をダウンロードします。

回路図を書く

回路図の左側の白い四角がFPGAです。各バンクごとにユニットを分けて作ってあります。真ん中のコンデンサーが各電源ピンにつながるパスコンです。コア用の電源から、各バンクのIOの電源、PLL用の電源などで30個近くあります。

右側の上部が、電源回路です。USBの5Vから3.3Vを生成します。50MHzのクロックも載せました。MAX10 FPGAの内蔵クロックは、FPGA内のPLLに接続できないので、水晶発振器による安定したクロック源が外部に必要です。

右側下段がIOピンがつながるピンヘッダになります。IOピンは全部で100ピン程度ありますが、ほぼ全てピンヘッダに引き出します。

MAX 10 FPGAの特殊な機能を持ったピンの説明や、プルアップ、プルダウンするのかなどは、「FPGA電子工作スーパーキット」の書籍の第2章に詳しく書いてあったので、それを参考にしました。この本は、よくまとまっていて、とてもいい資料ですね。

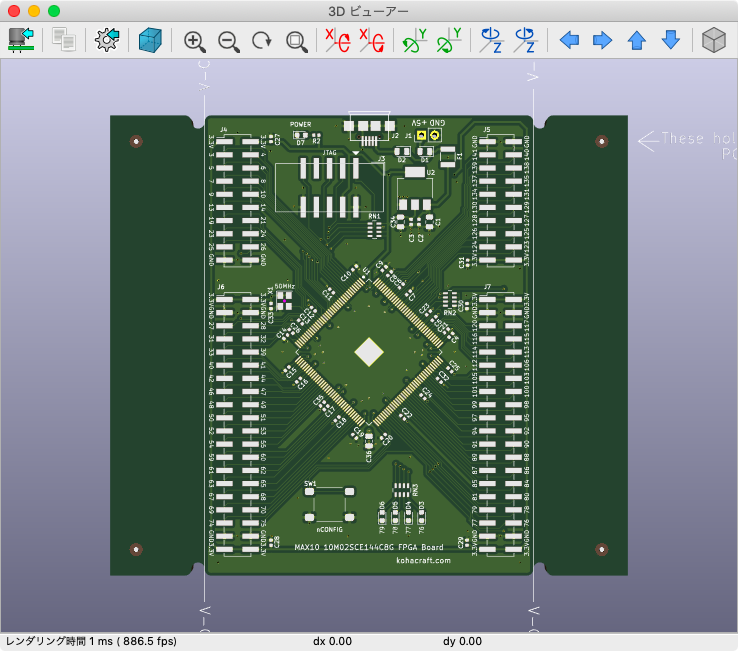

アートワーク

いつものように、部品を配置して、電源周りの重要な配線は手動で行い、残りの配線はオートルーターにお任せします。オートルーターが引いた配線を、もっと効率いいように手動で修正して、アートワーク完了です。

押しのけ配線が超便利

今回、KiCadで初めて、「押しのけ」配線を使ってみたのですが、とてもとても便利です。何本もあるバスの中に1本線を通すのが、超絶楽チンでした。是非ともオススメの機能です。

設定は、Pcbnewの[配線]->[インタラクティブルーターの設定]

[モード]を[押しのけ]に設定して、[OK]するだけです。

これで、バス配線の中をかき分けて、配線を通すことができます。隣の配線に触れると、その配線がよけてしまうので、普段から「押しのけ」していると配線しにくいですから、普段は「速度優先探索」の設定で使い、「押しのけ」て通したい時だけ、「押しのけ」の設定にするのがいいと思います。

データ完成

今回は、全て表面実装部品を使ってみます。ピンヘッダやJTAGのコネクタはスルーホールのタイプが普通なのですが、基板の裏側にピンが飛び出していて、実験中に基板の裏でショートするとよくないなと思い、ピンが基板の裏に出ない表面実装部品を初めて使ってみます。また、リフローだけですべての半田付けが完了するので、手間も軽減できますね。

基板の背面は、フラットです。

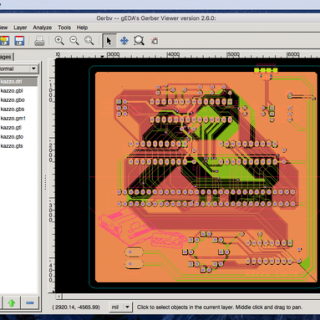

発注

いつものように、Seeed Stduio Fusion PCBに、基板とステンシルを発注します。 ガーバービューアーで、正しいファイルがアップロードされているか確認しておくと、安心です。

発注完了。2週間くらい待てば届くでしょうか。発送方法にOCSを選んだので、発送さえされれば数日で届きます。届くまでにFPGAも買っておかないとな。

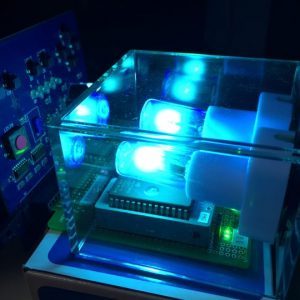

2019.7.10 続き 基板が届いたので、組み立てました。

このFPGAボードは↓↓こちら↓↓で販売しています。

コメント

電気回路を勉強しようと思い、このページを真似して作業しています。わかりやすい資料をありがとうございます。

ピンヘッダの空きピンは全てGNDにつなげばいいかと思っていましたが、なぜ+3.3Vに接続しているのでしょうか。

このさん

お役に立てて嬉しいです。

ピンヘッダから外付けの回路へ電気を供給できるよう、電源とGNDをピンヘッダに接続しています。