Intel CPLD MAX Vシリーズ

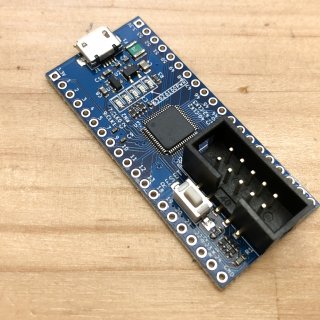

以前、Intel CPLDのMAX Vシリーズの5M160を使って、評価ボードを作りました。このボードは、全てのCPLDのピンを評価できるようにするために、全ピンをピンヘッダに出力していました。

今回は、CPLDのピンを全てではなく、できるだけ多くピンヘッダに出力しますが、ブレッドボードに刺して実験ができるような、細長い実験用ボードを作りたいと思います。

KiCadで設計

回路図

以前の回路を使い回し、ほぼ同じです。電源のレギュレータを小容量で小型のタイプに変更しました。

CPLDの出力ピンのうち、1〜24ピンと、34〜53ピンの36ピン分をピンヘッダに引き出しました。また60〜63ピンの4ピンをLEDに接続し、テストに使えるようにしています。

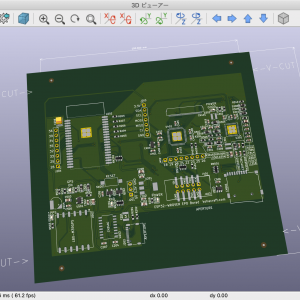

アートワーク

今回は、オートルーターで配線してみました。結構いい感じに配線できていそうです。

KiCadの使い方は、このトランジスタ技術に付属の冊子が、マニュアルとしてとても重宝します。

3Dビュー

基板の下方にあるJTAGのコネクタが結構大きく、基板の幅いっぱいを占めていますね。配置を縦向きにすれば、基板を細くできたかもしれません。

面付け

中国の一般的な基板製造屋さんでは、10cm×10cmのサイズまでは料金は変化しません。また、基板にVカットの溝を掘ってもらうには、基板サイズが7cm×7cm以上ないといけません。この基板1枚のサイズは3cm×5cmなので、7cm以上、10cm以下になるよう、3枚面付けしました。

ステンシルとの位置合わせの穴

基板の周囲の角には、ステンシルとの位置合わせのための、穴を開けておきます。基板には直径1mmの穴を開け、同じ位置に直径1mmのパッドを配置します。こうすることで、基板とステンシル両方の同じ位置に穴が開きます。ここに画鋲を刺すことで、基板とステンシルの位置合わせが簡単にできます。

ただし、ステンシルの注文の時に「Fiducials」の設定を「Etched Through」にしておく必要があります。初期設定では「No Fiducial」になっています。

データ的にステンシルに穴が開いていても、「No Fiducial」の設定の場合は、基板屋さんのオペレータがこの穴を無視する場合があり、ステンシルに穴が開きません。必ず「Etched Through」にしておきます。

設計完了

さて、基板の設計が完了しました。あとは注文するだけです。他の基板もまとめて発注したいので、それが完成してから発注したいと思います。

2020.5.15 追加

ブレッドボードの左右2ピンずつ使えるように、当初の基板よりもブレッドボード2ピン分、幅を狭くした基板に変更して、JLCPCBに発注しました。届くのが楽しみです。

2020.5.21追加 つづきはこちら

追加終わり

この商品はこちら👇👇👇で購入ができます。

コメント